Le microprocesseur possède

32 registres de 16 bits, notés r0 .. r31. Le registre r0 est

particulier : sa lecture renvoie toujours 0, par conséquent.

On pourra y écrire toute valeur qui doit être ignorée.

La taille des adresses est de 16 bits, ce qui permet de d'adresser 65636 mots de 16 bits

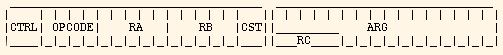

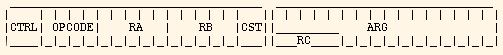

Le format des instruction est inspiré des instructions du mips

; toutes les instructions sont de la forme :

instr rA rB arg

où : rA et rB sont des registres, arg

est soit un registre soit une constante

Le codage est le suivant :

Description des champs :

CTRL (1 bit) : 1 si c'est une instruction de saut ou d'acces à

la mémoire, 0 si c'est une instruction arithmétique ou logique

OPCODE (4 bit) : code de l'instruction (cf plus loin)

RA (5 bits) : n° de rA

RB (5 bits) : n° de rB

CST (1 bit) : 1 si arg est une constante 0 sinon

RC (5 bits) : n° du registre correspondant à arg quand CST est à0

ARG (16 bits) : la constante arg si CST est à 1

Chaque instruction occupe donc 2 mots mémoires, de plus une instruction commence toujours à une adresse paire

Instructions de saut : jump0, ajump0

saut relatif : jump0

jump0 rA rB arg

provoque un branchement à l'adresse :

( adresse de l'instruction suivante ) + arg

si rB est à 0, et dans ce cas rA reçoit l'adresse

de l'instruction suivante

saut absolu : ajump0

ajump0 rA rB arg

provoque un branchement à l'adresse arg si rB est à 0,

et dans ce cas rA reçoit l'adresse de l'instruction suivante

Instruction de lecture et écriture en mémoire

lecture : read

read rA rB arg place dans le registre rA

le mot lu à l'adresse mémoire rB+arg

écriture : write

write rA rB arg écrit le contenu de rA à

l'adresse mémoire rB+arg

Instructions arithmétiques et logiques

Elles ont toutes le comportement suivant :

instr rA rB arg place dans rA le résultat de

instr( rB, arg) où instr(a,b)

est donné par le tableau suivant :

instr | champ OPCODE | instr(a,b) |

add | 1 0 0 0 | a+b |

sub | 1 0 0 1 | a-b |

or | 0 0 1 0 | ou bit ŕ bit |

and | 0 0 0 0 | et bit ŕ bit |

xor | 0 0 0 1 | ou exclusif |

nor | 0 0 1 1 | non ou |

shift | 0 1 0 0 | décalage d'un bit, |

comp | 1 0 1 1 | le bit de poids fort du résultat est ŕ 1 si |

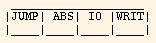

signification du champ OPCODE

dans le cas des instructions de saut et de lecture/ écriture:

JUMP : 1 si instructuction de branchement (jump0, ajump0)

ABS : 1 si c'est un saut absolu

IO : 1 si instruction de lecture/ecriture (read, write)

WRIT : 1 quand IO = 1 et l'instruction est write

Le micro possède 32 entrées et 32 sorties d'une largeur de 16 bits auxquelles on accède grace à la mémoire d'entrées/sorties

La mémoire est divisée en trois zones :

[ 0h - 200h [ : ROM Oh bien sûr )

[200h - 400h [ : Mémoire d'entrées/sorties200h + x, on envoie le

mot écrit sur la sortie n° (x mod 32) du micro, de même,

une lecture à une telle adresse permet d'accéder à

l'entrée correspondante[ 400h - 10000h [ : RAM L'adresse 200h est particulière : mettre à 1 le

bit de poids faible provoque un reset du microprocesseur ( saut à l'adresse 0

au prochain cycle ), ce que l'on peut aussi obtenir en plaçant à 1 le

bit de poids faible de l'entrée n° 0 du micro. Ecrire un 1 sur le second

bit plonge le processeur dans un profond sommeil dont il ne se réveille que par un

reset ; on obtient le même effet en mettant à 1 le second bit de

l'entrée n°.

Rmq : Les adresses 200h + (k * 20h) qui sont dans la mémoire I/O ont le

même comportement.